Skip to main content

3D IC Co-Design Methodology

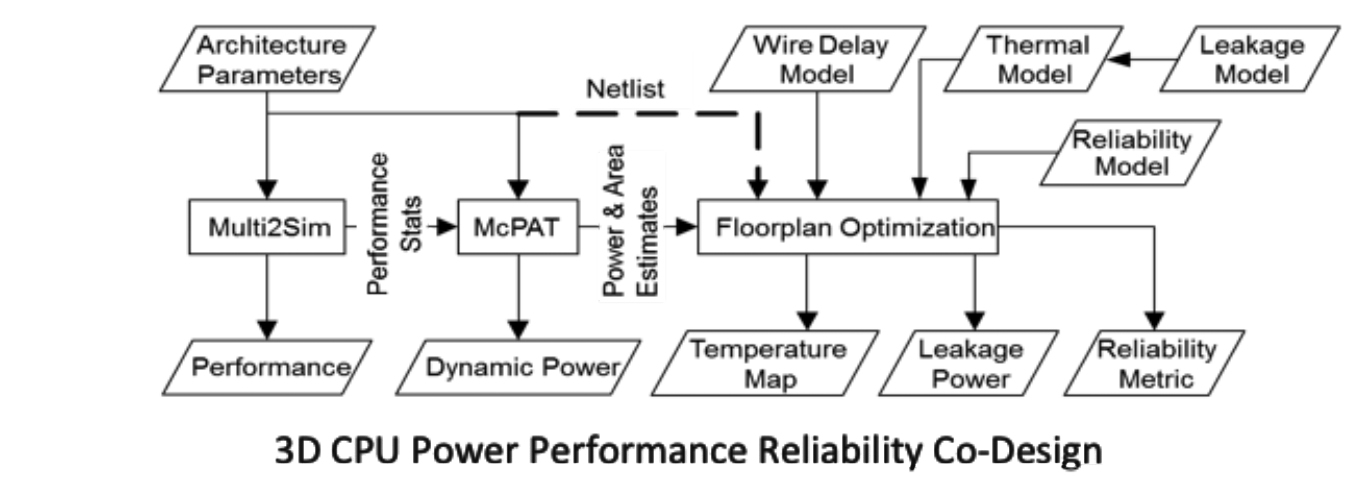

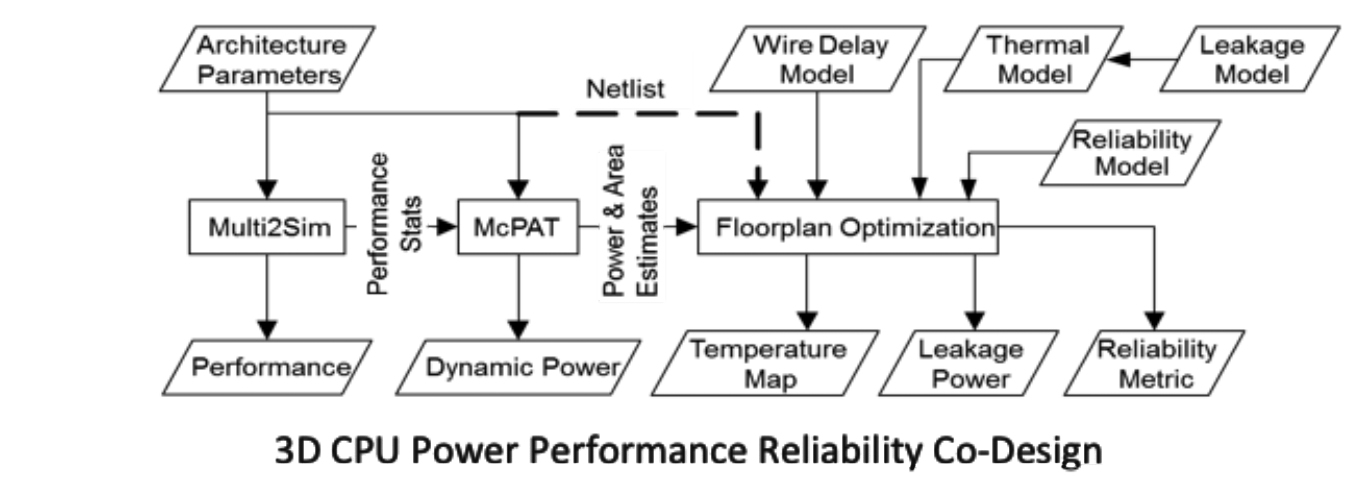

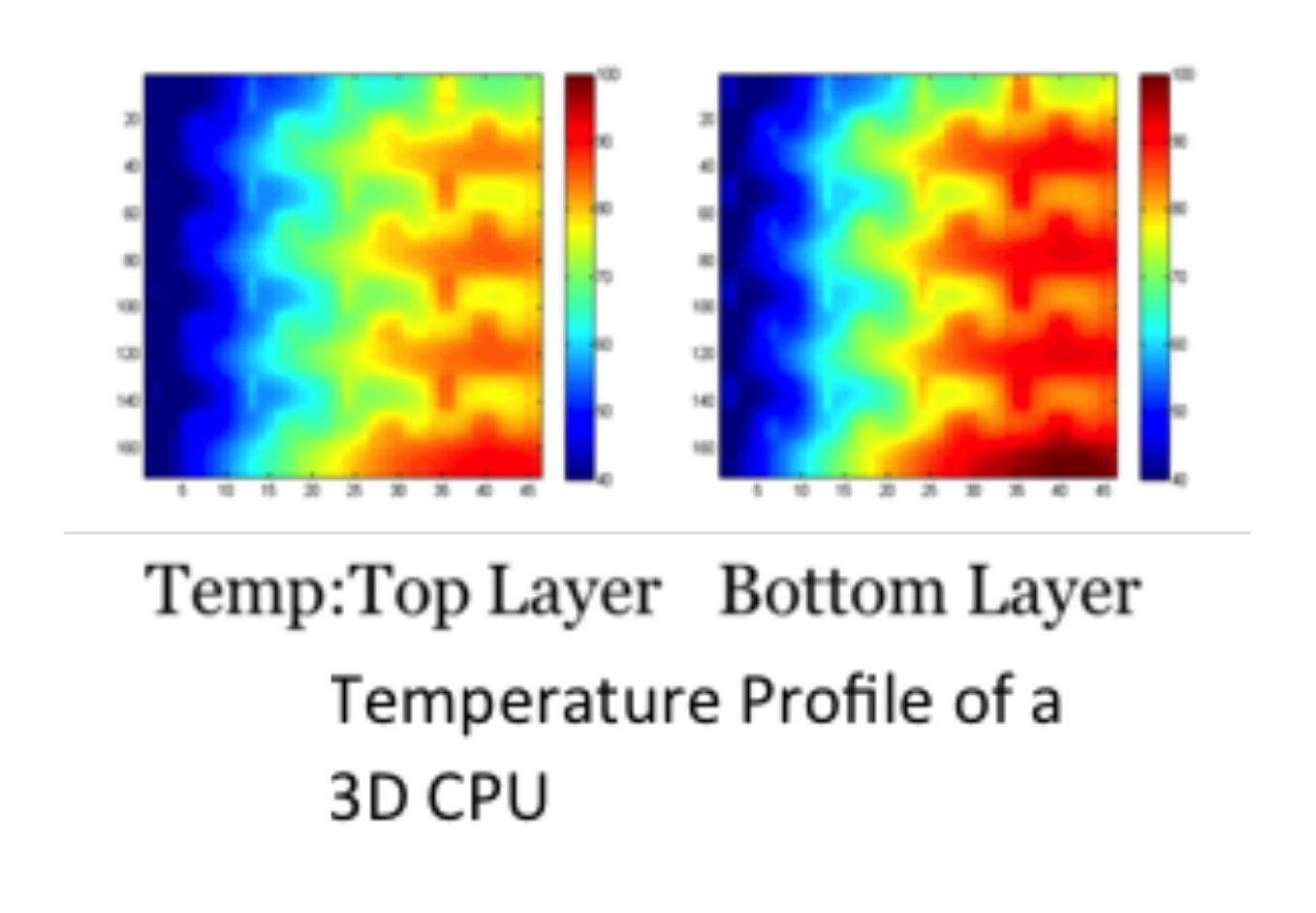

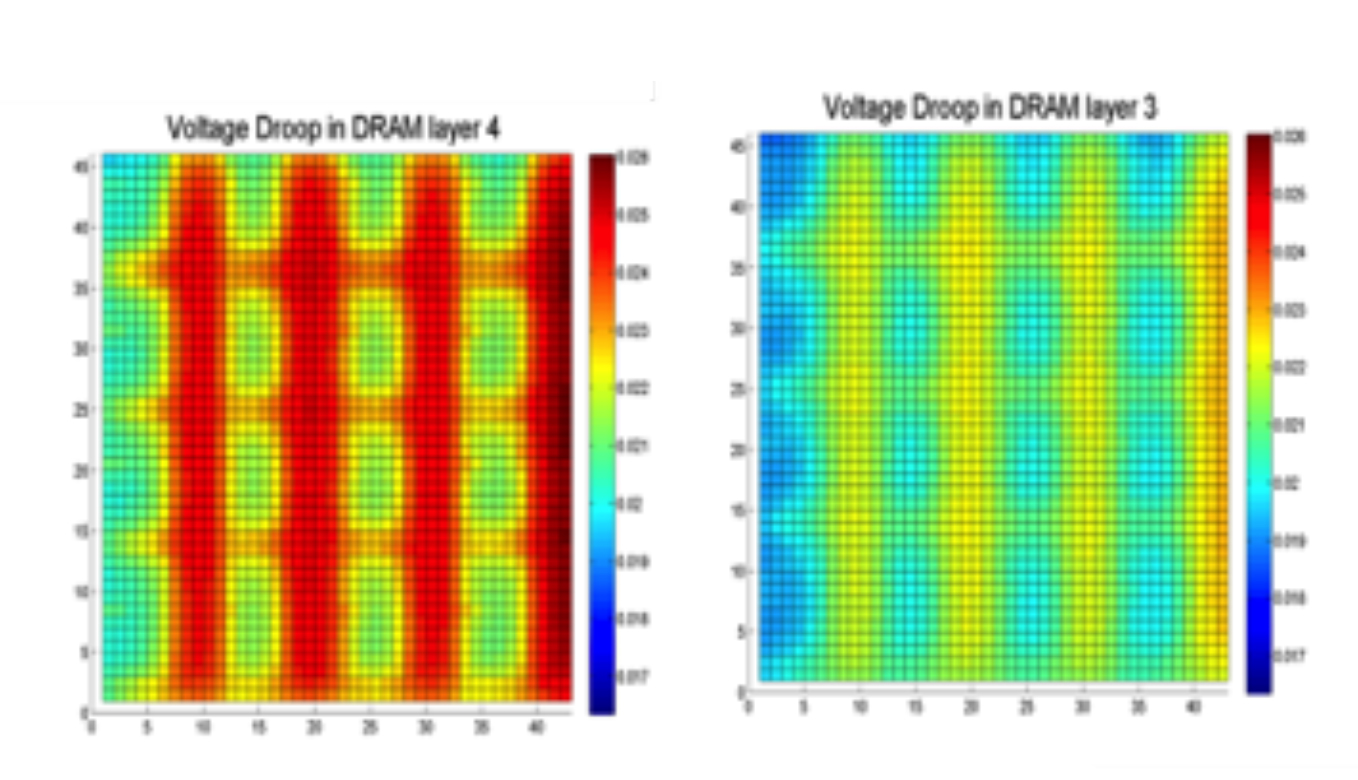

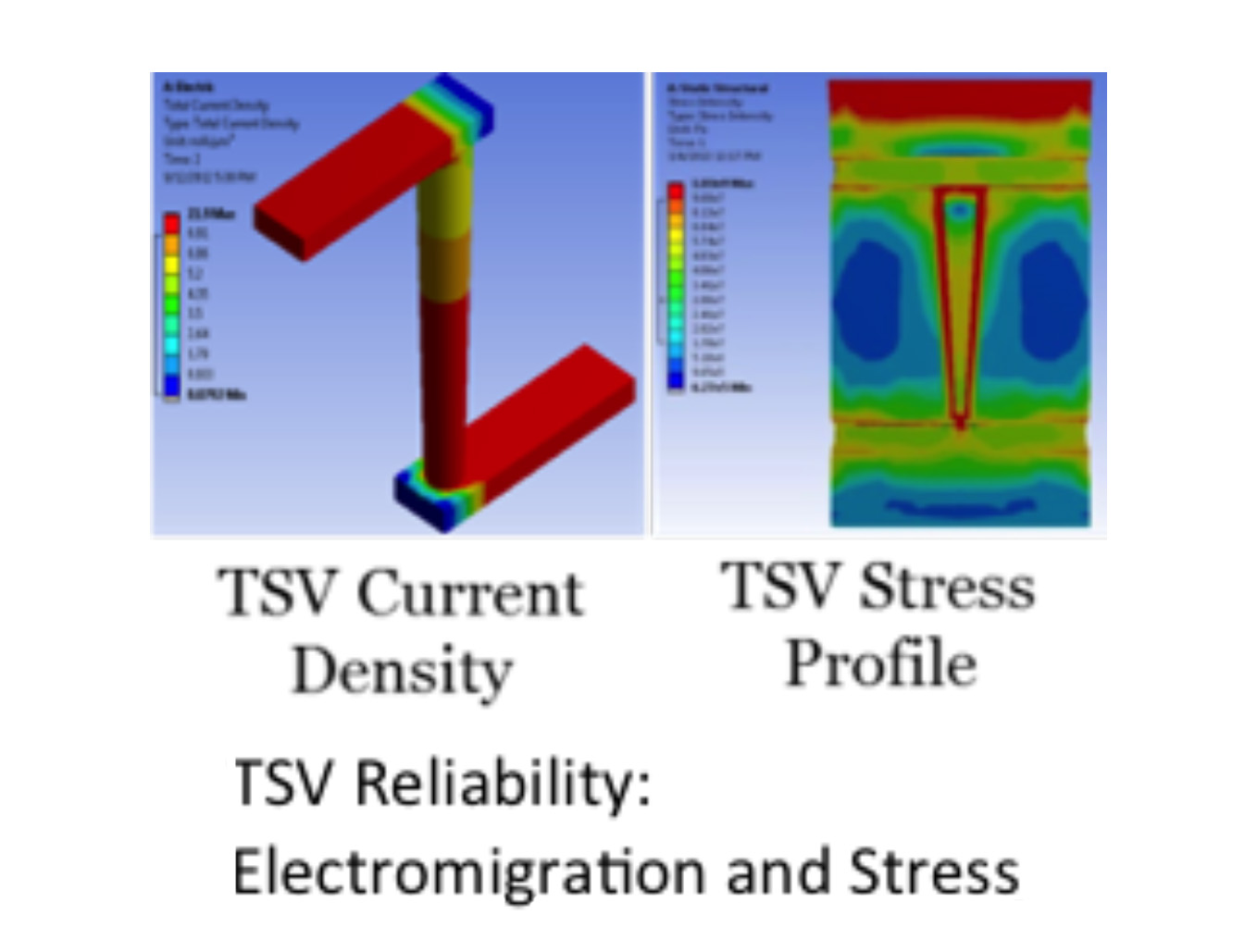

3D integration is a significant approach to achieving close integration of heterogeneous materials, devices, circuits and operation modalities. As 3D integration technology moves towards becoming a commercial reality, new design methods and tools are needed which allow co-integration of heterogeneous components and materials. In the context of 3D CPUs, we have done tremendous amount of work in putting together co-design tools which combine architectural aspects (pertaining to how instructions are executed and how memory and CPU interact), physical aspects (temperature and performance driven 3D floorplanning) and thermo-reliability aspects (modeling the thermal fields for different cooling solutions, electromigration based reliability loss in 3D TSVs, power delivery noise and TSV-TSV cross coupling). Our co-design framework was used to enable substantial improvements in performance and energy efficiency by accurately accounting for the interdependence between power performance and reliability for 3D CPU designs.

-

Tiantao Lu, and Ankur Srivastava, “Low-Power Clock Tree Synthesis for 3D-ICs”, To Appear, ACM Transactions on Design Automation of Electronic Systems (TODAES). 2017

-

Serafy, Z. Yang , A. Srivastava, Y. Hu and Y. Joshi, “Thermoelectric Codesign of 3-D CPUs and Embedded Microfluidic Pin-Fin Heatsinks”, IEEE Design & Test, vol. 33, no. 2, pp. 40-48, April 2016

-

Serafy, A. Bar-Cohen, A. Srivastava and D. Yeung, “Unlocking the True Potential of 3-D CPUs With Microfluidic Cooling,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 24, no. 4, pp. 1515-1523, April 2016

-

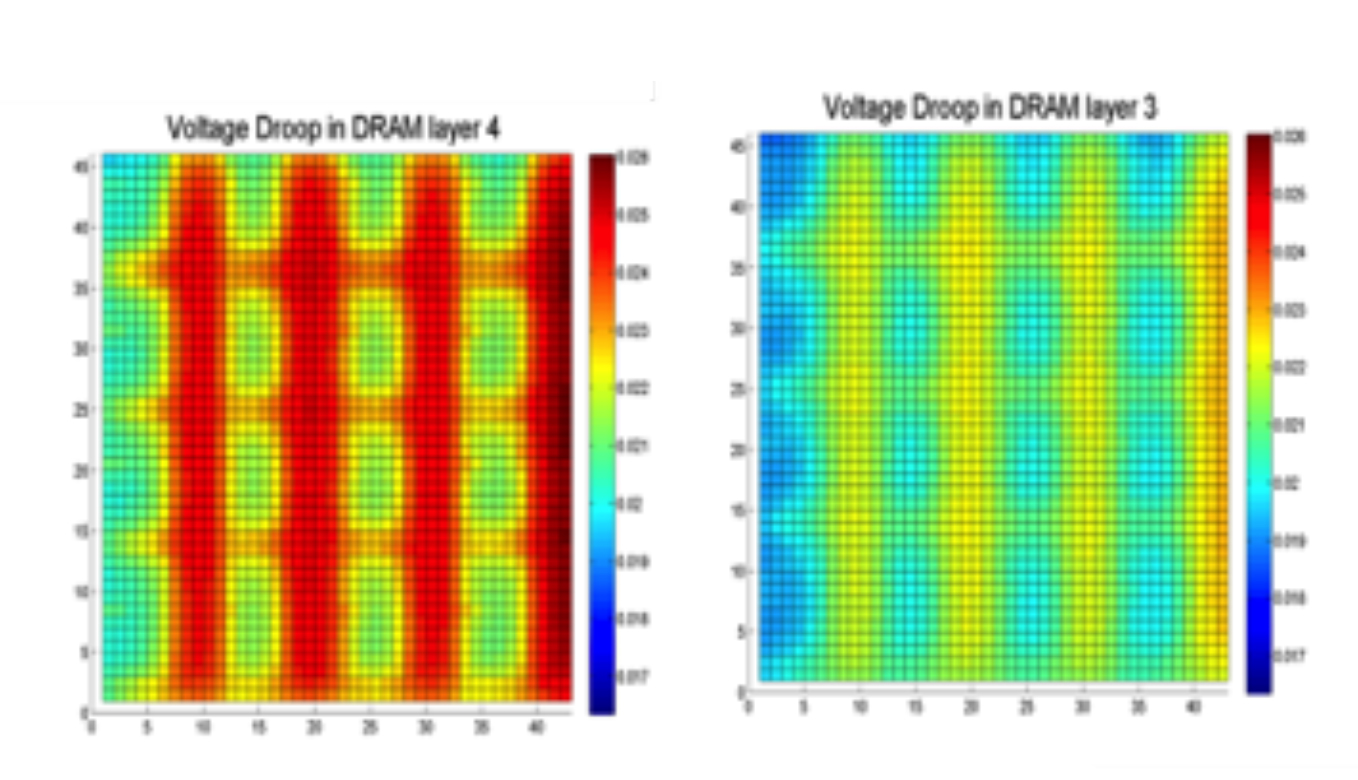

Lu, Tiantao, Caleb Serafy, Zhiyuan Yang and Ankur Srivastava. “Voltage Noise Induced DRAM Soft Error Reduction Technique for 3D-CPUs”. Proceedings of the 2016 International Symposium on Low Power Electronics and Design. ACM, 2016

-

Lu, Z. Yang and A. Srivastava, “Post-Placement Optimization for Thermal-Induced Mechanical Stress Reduction,” IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Pittsburgh, PA, July 2016, pp. 158-163.

-

Yang and A. Srivastava. “Physical Co-Design for Micro-Fluidically Cooled 3D ICs,” IEEE Intersociety Conference on Thermal and Thermo-mechanical Phenomena in Electronic Systems (ITherm), May 2016.

-

Yang, C. Serafy and A. Srivastava. “ECO Based Placement and Routing Frame-work for 3D FPGAs with Micro-Fluidic Cooling,” IEEE Field-Programmable Custom Computing Machines (FCCM), May 2016.

-

Lu, Z. Yang and A. Srivastava, “Electromigration-aware placement for 3D-ICs,” 17th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, 2016, pp. 35-40.

-

Serafy, T. Lu and A. Srivastava. “Thermal-Reliability Physical Co-Optimization During Architectural Design Space Exploration of 3D-CPUs.”, Proceedings of the Government Microcircuit Applications and Critical Technology Conference (GOMACTech). 2016.

-

Zhiyuan Yang, Ankur Srivastava, “Physical Design of 3D FPGAs Embedded with Micro-channel-based Fluidic Cooling,” In Proceedings of the ACM/SIGDA International Symposium on Field-Programmable Gate Arrays, 2016, (pp. 54-63).

-

Zhiyuan Yang, Ankur Srivastava, “Co-Placement for Pin-Fin Based Micro-Fluidically Cooled 3D ICs.” In ASME InterPACK, June 2015.

-

Lu, and A. Srivastava, “Electromigration-aware Clock Tree Synthesis for TSV-based 3D-ICs”, in Proc. IEEE/ACM Great Lakes Symposium on VLSI (GLSVLSI), May 2015

-

Lu, and A. Srivastava, “Electrical-thermal-reliability Co-design for TSV-based 3D-ICS”, in Proc. ASME InterPACK, 2015.

-

C. Serafy, A. Srivastava, A. Bar-Cohen and D. Yeung. “Design Space Exploration of 3D CPUs and Micro-Fluidic Heatsinks with Thermo-Electrical-Physical Co-Optimization.”, In Proceedings of the ASME International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems, 2015

-

Lu and A. Srivastava, “Modeling and Layout Optimization for Tapered TSVs,” IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 23, no. 12, pp. 3129-3132, Dec. 2015.

-

C. Serafy and A. Srivastava, “TSV Replacement and Shield Insertion for TSV–TSV Coupling Reduction in 3-D Global Placement,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 34, no. 4, pp. 554-562, April 2015.

-

Tiantao Lu and Ankur Srivastava, “Detailed Electrical and Reliability Study of Tapered TSVs”, Physical Design for 3D Integrated Circuits/Edited By Aida Todri-Sanial, Chuan Seng Tan, CRC Press 2015

-

Tiantao Lu and Ankur Srivastava, “Gated Low-power Clock Tree Synthesis for 3D-ICs”, International Symposium on Low Power Electronics and Design (ISLPED), page 319 – 322, August 2014.

-

Caleb Serafy, Ankur Srivastava, Donald Yeung, “Unlocking the True Potential of 3D CPUs with Micro-Fluidic Cooling,” Proceedings of the IEEE International Symposium on Lower Power Electronics and Design (ISLPED), August 2014

-

Caleb Serafy , Ankur Srivastava, “Leakage Power: Physical Mechanisms and Possible Solutions” Electronics Cooling , December 2014 (Magazine)

-

Bing Shi and Ankur Srivastava, Dynamic Thermal Management Considering Accurate Temperature-Leakage Interdependency”, Cooling of Microelectronic and Nanoelectronic Equipment, WSPC Series in Advanced Integration and Packaging, 2014

-

Caleb Serafy, Bing Shi, Ankur Srivastava, “A Geometric Approach to Chip-Scale TSV Shield Placement for the Reduction of TSV Coupling in 3D-ICs”, Elsevier Integration, the VLSI Journal: VLSI for the New Era, Volume 47 Issue 3, June 2014

-

Caleb Serafy, Ankur Srivastava, Donald Yeung, “Continued Frequency Scaling in 3D ICs through Micro-Fluidic Cooling”, Proceedings of the IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), May 2014

-

Serafy and A. Srivastava, “Coupling-Aware Force Driven Placement of TSVs and Shields in 3D-IC layouts”, ACM International Symposium on Physical Design, 201

-

C. Serafy and A. Srivastava, “Online TSV Health Monitoring and Built-in Self-Repair to Overcome Aging”, In Proceedings of the 15th IEEE Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, 2013(DFT}

-

C. Serafy, B. Shi, A. Srivastava and D. Yeung, “High Performance 3D Stacked DRAM Processor Architectures with Micro-Fluidic Cooling”, In Proceedings of the IEEE 3D System Integration Conference 2013 (3DIC).

-

T. Lu and A. Srivastava, “Detailed Electrical and Reliability Study on Tapered TSVs”, In Proceedings of the IEEE 3D System Integration Conference 2013 (3DIC).

-

Caleb Serafy, Ankur Srivastava, “A Geometric Approach to TSV Shield Placement for the Reduction of TSV-TSV Coupling in 3D-ICs”, Great Lakes Symposium on VLSI (GLSVLSI), May, 2013.

-

Bing Shi, Ankur Srivastava, “Co-optimization of TSV assignment and micro-channel placement for 3D-ICs”, Great Lakes Symposium on VLSI (GLSVLSI), May, 2013.

-

Bing Shi, Ankur Srivastava, “Thermal Stress Aware 3D-IC Statistical Static Timing Analysis”, Great Lakes Symposium on VLSI (GLSVLSI), May, 2013.

-

Bing Shi and Ankur Srivastava, “Micro-Fluidic Cooling for Stacked 3D-ICs: Fundamentals, Modeling and Design”, Advances in Computers / Edited by Ali Hurson, Vol. 88, Elsevier, 2013

-

INVITED: Avram Bar-Cohen, Ankur Srivastava and Bing Shi, “Thermo-Electrical Co-Design of 3D ICs: Challenges and Opportunities”, Computational Thermal Sciences, Begell House Publishers, Vol5, Issue 6, 2013

-

Bing Shi and Ankur Srivastava, “Optimized Micro-Channel Design for Stacked 3D ICs”, IEEE Transactions on Computer Aided Design 33(1):90-100 · December 2013

-

Bing Shi, Ankur Srivastava and Avram Bar-Cohen, “Co-design of Micro-fluidic Heat Sink and Thermal TSV for Cooling of 3D-IC”, IET Circuits, Devices & Systems Journal, Volume 7, Issue 5, September 2013

-

Bing Shi, Yufu Zhang and Ankur Srivastava,”Dynamic Thermal Management Under Soft Thermal Constraints”, IEEE Transactions on VLSI., Vol. 21, No. 11, November 2013

-

Bing Sh and Ankur Srivastava, “Thermal and Power-Aware Task Scheduling and Data Placement for Storage Centric Datacenters”, Handbook of Energy-Aware and Green Computing / Edited by Sanjay Ranka and Ishfaq Ahmad, Vol. 1, CRC Press, 2012

-

Bing Shi , Ankur Srivastava, Avram Bar-Cohen, “Hybrid 3D-IC Cooling System Using Micro-Fluidic Cooling and Thermal TSVs”, IEEE Computer Society Annual Symposium on VLSI (ISVLSI), August 2012

-

Bing Shi, Ankur Srivastava, “TSV-Constrained Micro-channel Infrastructure Design for Cooling Stacked 3D-ICs”, International Symposium on Physical Design (ISPD), April 2012.

-

Bing Shi, Ankur Srivastava, “Cooling of 3D-IC Using Non-Uniform Micro-channels and Sensor Based Dynamic Thermal Management”, invited paper, Forty-Ninth Annual Allerton Conference on Communication, Control, and Computing, Sept. 2011.

-

Bing Shi , Ankur Srivastava, “Non-Uniform Micro-Channel Design for Stacked 3D-ICs”, Proceedings of IEEE/ACM Design Automation Conference (DAC), June 2011